|

CROSS Technical Documentation User Manual and Technical Doc.

INFN Milano Bicocca

|

|

CROSS Technical Documentation User Manual and Technical Doc.

INFN Milano Bicocca

|

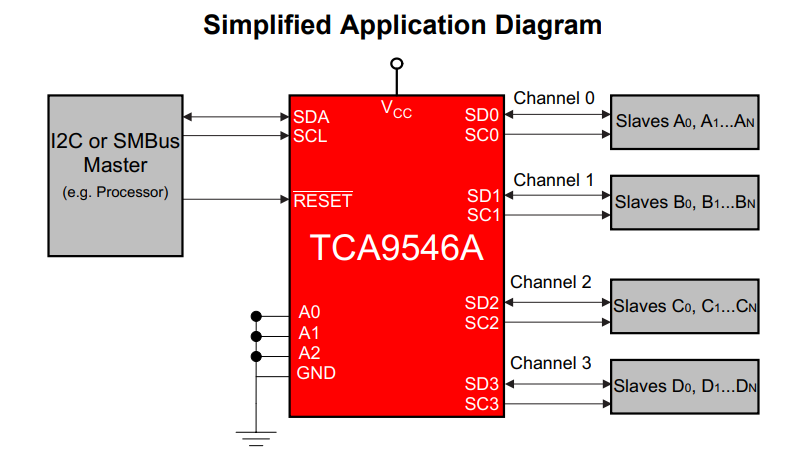

The mux which distributes the I2C in the board

SUMMARY:

The managing of this chip is made with only one function, the I2C_mux_select_ch() with input parameters: uint8_t scheda_su_scheda_giu, uint8_t I2C_mainboard, uint8_t canale_da_abilitare that allows to select which of the 4 possibile I2C channels has to be used. The scheme od the mux, the TCA9546APWR, is as in Figure_I2C_mux. It has a reset pin that is set as a first action at the call of the function. The chip has 4 I2C's to which send the input I2C. Thhe outpus can be individually activated or can be activated in parallel. Our choice is for the individual selection. Obviously, there is also the possibility to de-activate all the outputs.

The board manages 2 boxes so the first parameter scheda_su_scheda_giu is which of the boxes we want consider. scheda_su_scheda_giu can be 0 or 1.

The parameter canale_da_abilitare allows to select which of the 4 channels is to be enabled:

The parameter scheda_su_scheda_giu allows to select which of the 2 board to communicate:

Whenever the I2C is used, the I2C_mux must be set as a first step. Then, the I2C_mux is the last to be idled:

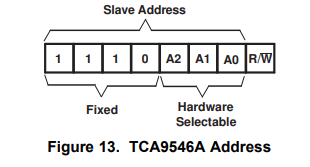

We set A0 to 1 in Figure_I2C_address_of_I2C_mux below and the I2C address of the chip is then (considering that the 3 MSb are fixed to 1) 0x71:

The address set on the mainboard is defined in:

The datasheet of the I2C mux is here: TCA9546A datasheet .

The codes for mamnaging the mux are:

br br