|

CROSS Technical Documentation User Manual and Technical Doc.

INFN Milano Bicocca

|

|

CROSS Technical Documentation User Manual and Technical Doc.

INFN Milano Bicocca

|

This chip is exploited to store the preamplifier parameters and settings

SUMMARY:

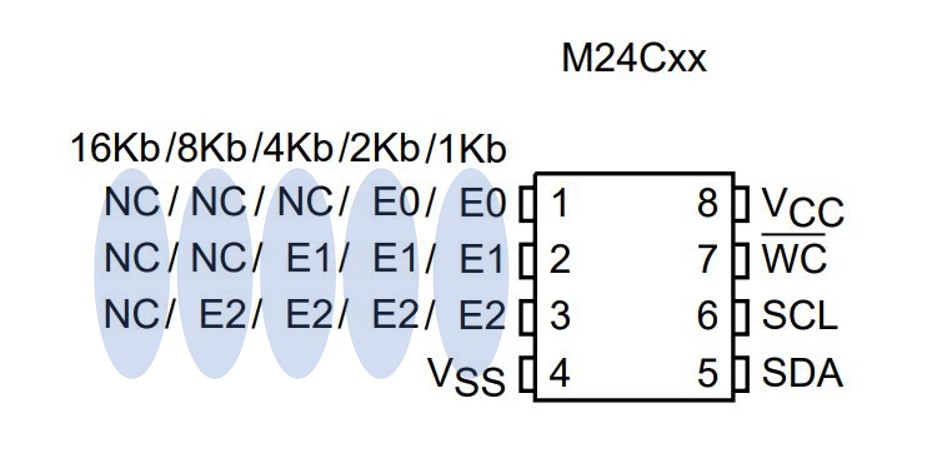

Each unit of the system has its own EPROM memory where to store at least its sn and, when present, the fw version. The first samples of the preamplifier has the MC24C08, that is a 8 Kb I2C flash memory. The frontend board has a MC24C16. Finally the postfrontend board has the MC24C64. The different memory sizes have different cell address organization. From 1Kb up to 16Kb they are shown in figure Figure_M24C00_16K. Namely, depending on the size, the 8-LSb bits are in the first word sent, while the MSb in excess of 8 are in the first bits of the I2C addres, so that the larger is the size, the lesser is the available choice left for the I2C addres (4 of the 7 I2C address bits are fixed). Different is the approach for the M24C32 and M24C64 that uses 2 bytes of data for addressing and have the 3 available bits free for I2C address, the case 1 KB in Figure_M24C00_16K.

In our frontend we are going to use the M24C32 for both the preamplifier and the frontend board and the M24C64 in the post frontend board. The different choices are only due to the availability at the moment of the population of the boards. Both memories requires a 2-bytes address.

An example of use of 4-bytes writing of the 32k/64K EPROM at addres 0x20 of the channel6 EPROM is here:

br

There are a number of variables and definitions to manage the memories, but the the functions to use are only 2 and very simple. To read from the memory we use EPROM_lettura_M24C32_64(uint8_t scheda_su_scheda_giu,uint8_t I2C_mainboard,uint8_t canale, short indirizzo_memoria , uint8_t *dati_letti), while to write EPROM_scrittura_M24C32_64(uint8_t scheda_su_scheda_giu, uint8_t mainboard_postmainboard , uint8_t canale, short indirizzo_memoria , uint8_t *dati_da_scrivere).

scheda_su_scheda_giu is one of the 2 boards to select, canali is the preamplifier memory or the frontend board memory, according to the following enum canali_eprom:

indirizzo_memoria is the address of the memory to write to or to read from and *dati_da_scrivere the pointer to the data to read/write. Take care: only 4 bytes can be read or written for each call.

The state condition of the channel cane be recordered and aplied in a differenta ways. The variables that reflect the state are stored in 2 memory loactions.

The first state is that recalled at startup. This state requires that the PGA gain is 1 and that the preamplifier is connected to GND. The memory location for this state is Memory_preamplifier_startup_offset_trimmer. Note that at sturtup this state is applied only if the memory location Memory_preamplifier_startup_offset_trimmer_ON_0_OFF_ff is set to 0 value. This is done by the sw at the time the storing takes place. The state can be called also by setting the corresponding bit, but take care that for this case gain and detector state are not resumed and the user must do it. The startup state is created at the end of the offset adjustment, if the corresponding flag is set.

Another possible state is the user state. In this case it is stored at Memory_preamplifier_user_offset_trimmer and Memory_preamplifier_user_detector_and_gain which reflect the full condition for the channel, both offset, gain and detector condition. This state can be stored in 2 ways. After offset adjustment by setting the corresponding bit, or by a picture of the state, with no other actions than the storing of the variables, by setting the corresponding bit.

The state can be recovered by the corresponding bit and this work only if the Memory_preamplifier_user_offset_trimmer_ON_0_OFF_ff was set to 0. This is done by the sw at the time the storing takes place.

The bits to set are in the instr_output_offset_to_be_set, at the Byte3 option.

The function invoked is the following:

Concerning the functions which are able to work with the EPROM having size smaller or equalt o 16Kb we have that the reading function is here:

While the writng function is here:

There are 4 different I2C channels (selected at I2C_mux_select_ch()) and 2 I2C addresses are exploitable for the preamplifier EPROMs: EPROM_I2C_addres_memory_ch_pari and EPROM_I2C_addres_memory_ch_dispari, while the onboard EPROM is at EPROM_mainboard_I2C_addres. The I2C paremeters for each EPROM are in the structure address_detector_bias_trimmer_type:

So that the 7 positions strucure is EPROM_address.

The codes for I2C_0 is at:

Here the list of the locations of preamplifier EPROM, remember to multiply by 4, or <<2, the bullet number to set the actual address, an unsigned int:

The last memory cell used is #Memory_preamplifier_last_memory_used. If it not coincide with the length of the list above it means that the list is not upgraded.

Here the list of the locations of mainboard EPROM, remember to multiply by 4, or <<2, the bullet number to set the actual address, an unsigned int:

Here the list of the locations of post-mainboard EPROM, remember to multiply by 4, or <<2, the bullet number to set the actual address, an unsigned int:

Memory_postmainboard_last_memory_used_first_free.